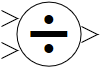

Делитель

|

|

| Векторный | Си

| ST | |

| в палитре | на схеме |

Описание

Блок векторизован, реализует деление входных сигналов блока (при скалярных сигналах на входе):

где y(t) – выходной скалярный сигнал блока; u1(t), u2(t) – входные сигналы; или поэлементное деление входных величин блока (при векторных сигналах на входе):

где yi(t) – i-ый элемент выходного векторного сигнала блока y(t); u1 i(t), u2 i(t) – i-ые элементы первого и второго входных сигналов, u1(t), u2(t) – размерность входов и выхода.

Обязательным условием является неравенство делителя нулю (u2 i(t)≠0)!

Входные порты

| Имя | Описание | Тип линии связи |

|---|---|---|

| dividend | Порт для значения u1. | Математическая |

| devider | Порт для значения u2. | Математическая |

Выходные порты

| Имя | Описание | Тип линии связи |

|---|---|---|

| result | Порт для результата операции деления. | Математическая |

Свойства

| Название | Имя | Описание | По умолчанию | Тип данных |

|---|---|---|---|---|

| Максимальное значение при делении числа на 0 | fMaxOut | Значение выхода блока при делении на 0. | 1e20 | Вещественное |

| Сигнализировать о делении на 0 | fshowdiverr | Выдавать или нет сообщение о том, что в блоке произошло деление на 0. | Да | Двоичное |

Параметры

Блок не имеет параметров.

Прим.:

Размерность выходного сигнала всегда равна размерности входных сигналов. Блок формирует

скалярный выходной сигнал при скалярных входных сигналах. Если входные сигналы векторные, то

их размерности должны совпадать.