Алгоритм кодирования IRA LDPC кодов

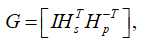

Проверочная матрица нерегулярного кода повторения-накопления (англ. IRA) состоит из двух частей - разреженной матрицы перестановок H s размерностью kldpc x mldpc и ступенчатой матрицы H p размерностью mldpc x mldpc, где kldpc – число бит в информационном слове, mldpc – число проверок. Такая структура кода позволяет получить порождающую матрицу вида:

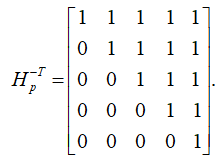

с помощью которой осуществляется процедура кодирования. Матрица Hp-T является верхней треугольной:

Алгоритм кодирования заключается в умножении информационного вектора на проверочную матрицу H p -T что эквивалентно накоплению результата в простейшем аккумуляторе.

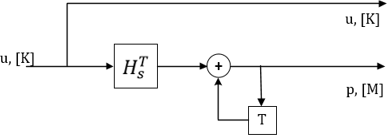

Однако получение порождающей матрицы не обязательно, поскольку все необходимые вычисления для кодирования могут быть реализованы в соответствии со схемой кодера по проверочной матрице H представленной на рисунке:

Более подробное описание данного алгоритма LDPC кодирования представлено в [1].

Список источников

- European Telecommunications Standards Institute, "Digital Video Broadcasting (DVB); Second generation framing structure, channel coding and modulation systems for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications; Part 1: DVB-S2", European Telecommunications Standards Institute, ETSI EN 302 307-1 V1.4.1, November 2014.

- LDPC кодер.

- Стандарт AList