LDPC-кодер преобразует битовое сообщение i длины kldpc в кодовое слово c = [ i, p ] длины nldpc, где p - проверочные биты, определяющиеся представленным ниже алгоритмом кодирования.

Входное информационное слово обрабатывается в блоках по z бит, представимых в виде векторов-столбцов, число которых составляет kb = kldpc / z. Выходное проверочное слово также представляется в виде mb = (nlpdc - kldpc) / z векторов по z бит.

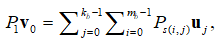

Обработка данных LDPC-кодером выполняется в два этапа. На первом этапе происходит расчёт первого вектора проверочной части v0 , определяемого формулой:

где Pk при k ≥ 0 является циклической матрицей размера z × z, строка с номером Z (Z ∈ {0, …, z - 1}) которой получается с помощью циклического сдвига на Z позиций вправо строки с единственным ненулевым элементом в позиции k, а при k = -1 является нулевой матрицей размера z × z.

Расчёт на первом этапе производится с помощью mb сдвиговых регистров длины z. На шаге j (j ∈ {0, …, kb - 1}) в каждый из регистров загружается блок u j , после чего в каждом регистре производятся сдвиги: в регистре с номером i циклический сдвиг влево составляет s(i, j), если s(i, j) ≥ 0; при s(i, j) = -1 регистр обнуляется.

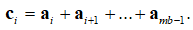

Значение каждого регистра аккумулируется в промежуточном буфере a i (i = 0, …, mb - 1) длины z, инициализируемом нулевым значением перед обработкой нового информационного слова i . После выполнения kb операций «сдвиг-суммирование» происходит формирование векторов промежуточного результата c0, c1, … cmb - 1: вектор c i содержит сумму буферов с номерами от i до mb - 1:

Вектор v 0 получается циклическим сдвигом на 1 позицию вправо вектора c 0 .

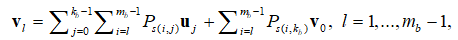

На втором этапе выполняется вычисление векторов проверочных бит v 1 , v 2 , … v mb - 1 , определяемых выражением:

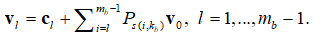

причём для подсчёта используется следующая формула:

На каждом шаге l (l ∈ {1, …, mb - 1}) выполняется вычисление вектора проверочных бит v l сложением вектора c l и частичной суммы циклических сдвигов вектора v 0 согласно значениям столбца 0 с номерами от i до mb - 1 матрицы H b2 .

Сопутствующие материалы:

- Структура проверочной матрицы квазициклических QC-IRA LDPC кодов.

- 802.11-2016 - IEEE Standard for Information technology-- Local and metropolitan area networks — Specific requirements — Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications // IEEE, New-York, USA. - 2016, December.

- LDPC кодер.

- Стандарт AList.