Скремблер

|

|

|

| в палитре | на схеме |

Описание

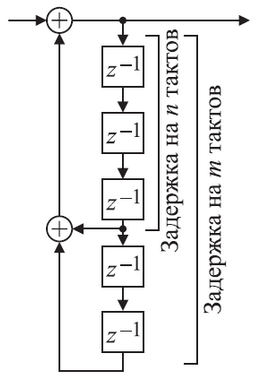

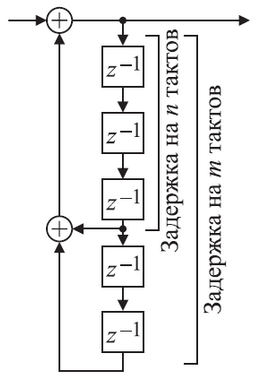

Блок предназначен для скремблирования входного битового сигнала с целью придания ему свойств

случайной последовательности [1]. Алгоритм работы

скремблера с задающим полиномом [n, m] может быть схематично представлен в виде

структурной схемы:

Инициализирующая последовательность регистра сдвига и полином скремблера задаются

пользователем. Доступны два режима работы блока:

- Обычный режим – инициализирующая последовательность регистра сдвига задается в свойствах блока и не изменяется на протяжении работы скремблера. При подаче единичного сигнала на порт "reset" (порт добавляется опционально в свойствах блока) блок возвращает ячейки памяти регистра сдвига к первоначальному состоянию.

- Режим переинициализации – инициализирующая последовательность регистра сдвига задается через дополнительный порт "init bits" и может изменяться в процессе работы скремблера. При подаче единичного сигнала на порт "reset" блок считывает новую инициализирующую последовательность из порта "init bits" и устанавливает ячейки памяти регистра сдвига в это состояние.

Входные порты

- in bits – входной скалярный сигнал;

- init bits – входной вектор переинициализации регистра сдвига;

- reset – вход для сигнала сброса ячеек регистра сдвига.

Выходные порты

- out bits – выходной скремблированный сигнал.

Свойства

- Массив ненулевых коэффициентов полинома – задающий полином скремблера, задается в виде массива номеров ненулевых коэффициентов;

- Режим переинициализации – флаг включения/отключения режима динамической переинициализации;

- Сброс – флаг включения/отключения входа сброса (свойство доступно только при отключенном режиме динамической переинициализации);

- Инициализирующая последовательность – вектор значений ячеек регистра сдвига, задается в виде десятичного числа, соответствующего двоичной последовательности (свойство доступно только при отключенном режиме динамической переинициализации).

Параметры

Блок не имеет параметров.

Сопутствующие материалы

- Скляр Б. Цифровая связь. Теоретические основы и практическое применение: пер. с англ.— М.: Издательский дом "Вильямс", 2003