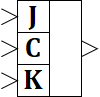

JK-триггер

|

|

| Векторный | Си

| |

| в палитре | на схеме |

Описание

Блок реализует модель JK-триггера с синхронизирующим входом С, т.е. при спаде сигнала на входе C блок работает аналогично RS-триггеру с одним отличием: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное.

Таблица истинности JK-триггера спаде сигнала на входе C представлена ниже.

| J | K | y(t) |

|---|---|---|

| 0 | 0 | y(t–Δt) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | y̅(t–Δt) |

где y(t–Δt) и y(t) – выходные сигналы блока на предыдущем и текущем шагах интегрирования соответственно.

В противном случае блок сохраняет предыдущее состояние выхода вне зависимости от значений сигналов на входах J и K.

Входные порты

| Имя | Описание | Тип линии связи |

|---|---|---|

| J | Входной порт установки. | Математическая |

| C | Входной порт синхронизации. | Математическая |

| K | Входной порт сброса. | Математическая |

Выходные порты

| Имя | Описание | Тип линии связи |

|---|---|---|

| out | Выходной порт триггера. | Математическая |

| Yinv | Инверсный выходной порт (опционально добавляется в свойствах блока). | Математическая |

Свойства

Параметры

Блок не имеет параметров.