|

|

|

| в палитре | на схеме |

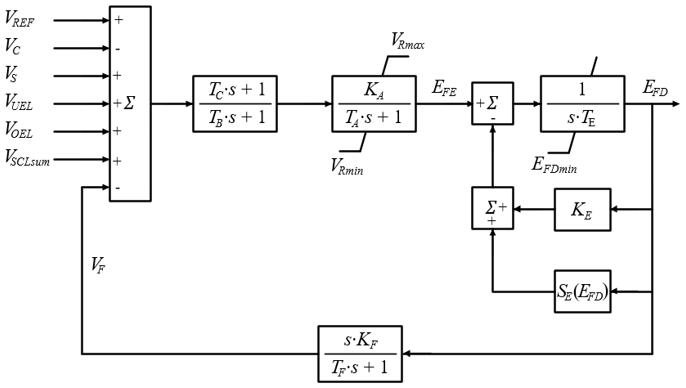

Блок реализует модель системы возбуждения типа DC1С в соответствии с IEEE 421.5-2016, и предназначен для использования с блоками «ЭЦС – Генератор синхронный» и «ЭЦД – Генератор синхронный».

Рисунок 1. Блок схема системы возбуждения типа DC1C

Основным входным сигналом для модели служит сигнал уставки VREF. Уставка VREF сравнивается с сигналом VC от преобразователя конечного напряжения и компенсатора нагрузки (в модели типа DC1C в качестве сигнала VC принимается напряжение статора генератора VT без промежуточных преобразований). Выходным сигналом модели является напряжение возбуждения ЕFD.

Рисунок 2. Структура двунаправленной шины блока «ЭЦ - Система возбуждения (type IEEE DC1C)»

В модели предусмотрены дополнительные входные порты сигналов, которые могут поступать от моделей (при их наличии): ограничителя перевозбуждения VUEL, ограничителя недовозбуждения VOEL, ограничителя по току статора VSCLsum и стабилизации энергосистемы VS. При необходимости внешнего задания этих сигналов, свойству «Показывать порты ограничителей» нужно присвоить значение «Да», после чего у него появятся соответствующие входные порты. Значение неподключенного порта равно 0.

Входные порты

- Vref – уставка напряжения статора генератора;Прим.: Vref задается в о.е. номинального напряжения генератора. Значение уставки должно быть ≥ 0

- Vs – сигнал от модели стабилизатора энергосистемы, о.е;

- Vuel – сигнал от ограничителя минимального возбуждения, о.е;

- Voel – сигнал от ограничителя максимального возбуждения, о.е;

- Vscl sum – сигнал от ограничителя по току статора, о.е.

Выходные порты

- G – порт многоканальной связи с генератором.

Свойства и их рекомендуемые значения

- Коэффициент усиления выхода регулятора (Ka) — 46*

- Постоянная времени выхода регулятора, с (Ta) — 0.06*

- Постоянная времени запаздывания регулятора, с (Tb) — 0**

- Постоянная времени опережения регулятора, с (Tc) — 0**

- Максимальное значение выхода регулятора, о.е. (Vrmax) — 1*

- Минимальное значение выхода регулятора, о.е. (Vrmin) — -0.9*

- Коэффициент пропорциональности напряжения возбудителя (Ke) — ***

- Постоянная времени возбудителя, с (Te) — 0.46*

- Минимальное напряжение возбуждения, о.е. (Efdmin) — -99*

- Характеристика насыщения: напряжения [E1, E2], о.е. (Ef) — [2.3, 3.3]*

- Характеристика насыщения: коэффициенты [SE1, SE2] (Se) — [0.1, 0.33]*

- Коэффициент усиления канала обратной связи (Kf) — 0.1*

- Постоянная времени канала обратной связи, с (Tf) — 1*

- Показывать порты ограничителей (Port_on) — Да/Нет

* Рекомендовано стандартом IEEE 421.5-2016 Recommended Practice for Excitation System Models for Power System Stability Studies.

** Если постоянные времени "Постоянная времени запаздывания регулятора, с" и "Постоянная времени опережения регулятора, с" задаются, то рекомендуется присваивать им значения больше минимального шага интегрирования или уменьшить шаг интегрирования. Если постоянные времени равны или каждая меньше минимального шага, то выход данного звена приравнивается входу.

***Коэффициент определяется из начальных условий.