|

|

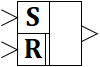

| Векторизован | Си | |

| в палитре | на схеме |

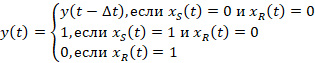

Блок реализует модель RS-триггера с приоритетом по сбросу, т.е. если уровень логической единицы присутствует на входах R и S, то выход принимает значение логического нуля:

Входные порты

- S – входной порт установки триггера;

- R – входной порт сброса триггера.

Выходные порты

- out – выходной порт триггера;

- Yinv – инверсный выходной порт (опционально добавляется в свойствах блока).

Свойства

- Начальные условия – начальные значения выходного логического сигнала;

- Добавить инверсный выход – указывает наличие инверсного выхода.

Параметры

нет